服務(wù)熱線

0755-83044319

發(fā)布時間:2024-09-19作者來源:薩科微瀏覽:1579

1. DRAM的基本概念

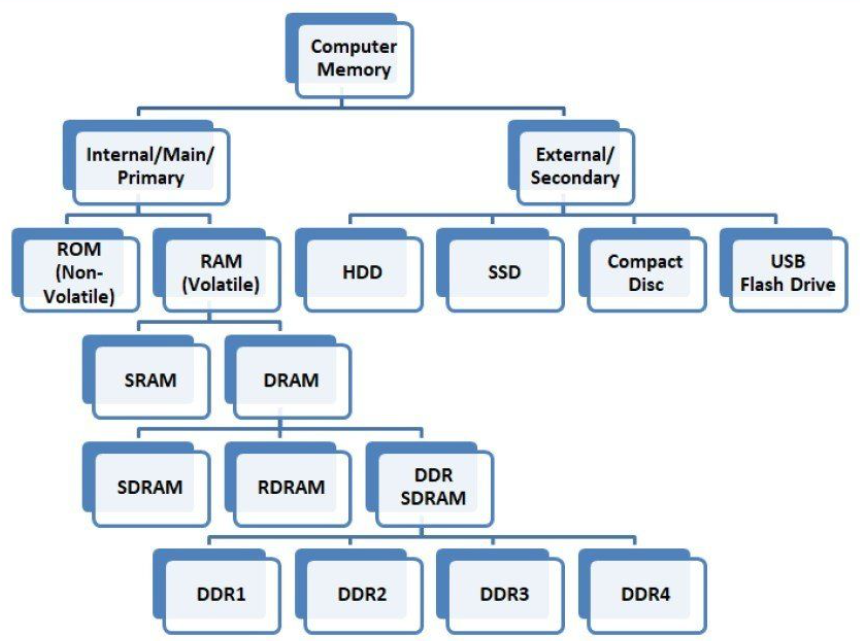

DRAM(Dynamic Random-Access Memory)是一種存儲數(shù)據(jù)的半導(dǎo)體器件,廣泛應(yīng)用于計(jì)算機(jī)和其他電子設(shè)備中。

圖:存儲芯片分類

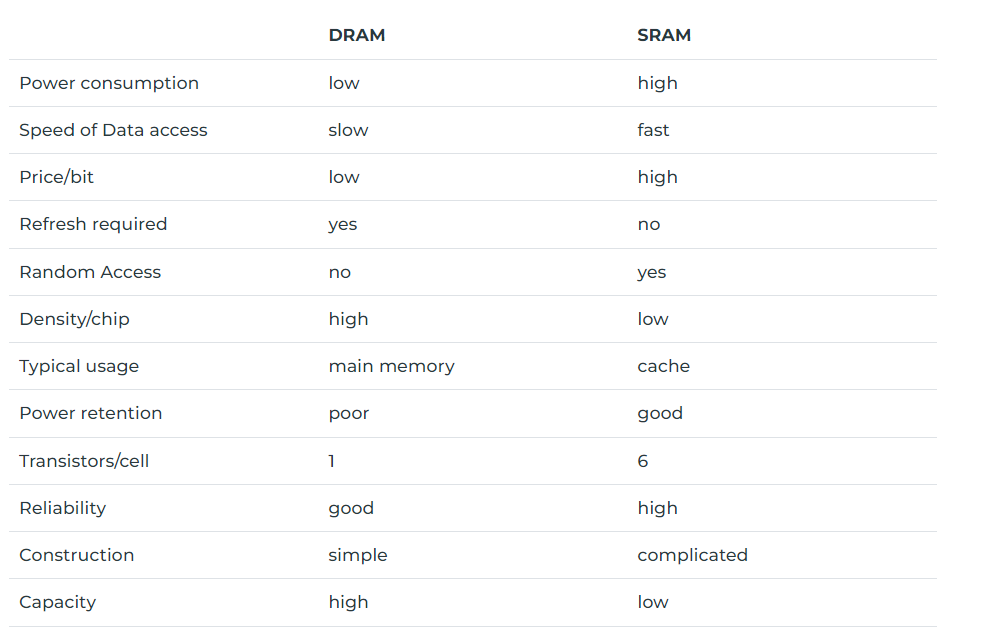

與SRAM(靜態(tài)隨機(jī)存取存儲器)不同,DRAM需要周期性地刷新來保持存儲的數(shù)據(jù),這就是“動態(tài)”的含義。每個DRAM單元由一個電容器和一個晶體管組成。

圖:DRAM和SRAM優(yōu)劣勢對比

圖:利用DRAM做成的內(nèi)存條

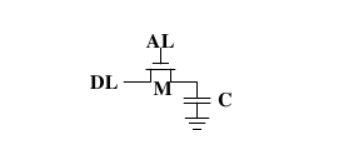

2. DRAM單元結(jié)構(gòu)

每個DRAM存儲單元主要由兩個部分構(gòu)成:

電容器:用于存儲數(shù)據(jù),電容器可以充電(表示“1”)或放電(表示“0”)。

晶體管:作為開關(guān),用于控制電容器的充放電狀態(tài),從而讀寫數(shù)據(jù)。

圖:DRAM單元結(jié)構(gòu)

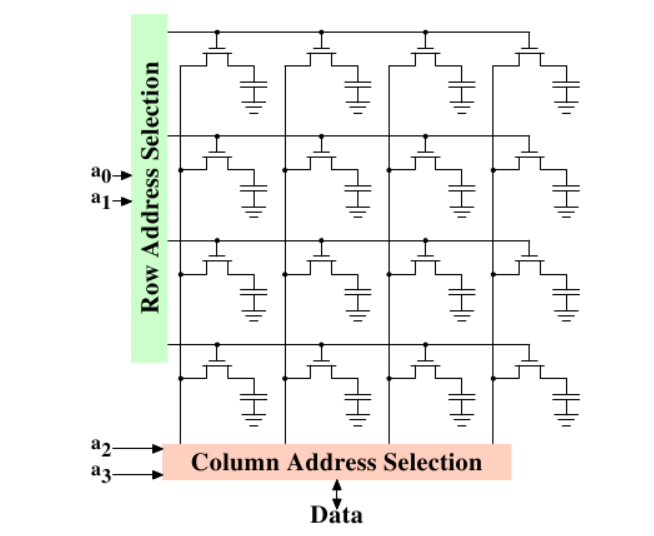

3. 數(shù)據(jù)存儲原理

寫入數(shù)據(jù):當(dāng)需要寫入數(shù)據(jù)時,電路會通過晶體管控制電容器的充放電狀態(tài),將“1”或“0”寫入存儲單元。

讀取數(shù)據(jù):讀取操作時,通過控制晶體管,將電容器中的電荷狀態(tài)(電壓)讀出,判斷是“1”還是“0”。

圖:DRAM結(jié)構(gòu)

4. 刷新操作

由于電容器存在漏電現(xiàn)象,電荷會逐漸消散。因此,DRAM需要定期刷新(通常每隔幾毫秒)來重新充電,從而保持?jǐn)?shù)據(jù)的正確性。這一操作由專用的刷新電路完成。

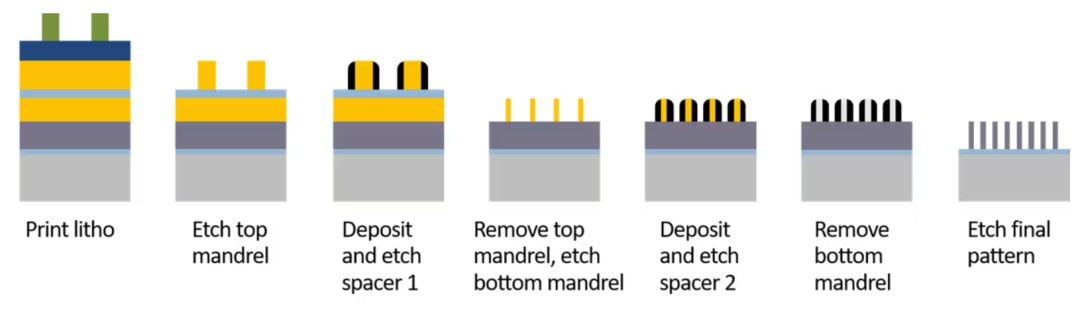

5. DRAM的工藝挑戰(zhàn)

工藝縮減:隨著技術(shù)節(jié)點(diǎn)的縮小(如從38nm到19nm再到更小節(jié)點(diǎn)),每個存儲單元的尺寸大幅減小,這給晶體管和電容器的制造帶來了巨大的挑戰(zhàn)。需要精確控制蝕刻、氧化、摻雜等工藝步驟,以確保單元的可靠性和性能。

設(shè)計(jì)規(guī)則縮減:設(shè)計(jì)規(guī)則的縮減要求更嚴(yán)格的布局和布線,以避免干擾和信號完整性問題。

漏電控制:工藝優(yōu)化中,特別關(guān)注晶體管的漏電控制,以提高DRAM的效率和可靠性。

圖:多次曝光工藝流程

6. DRAM的可靠性和性能優(yōu)化

可靠性:通過優(yōu)化工藝參數(shù)(如離子注入條件、熱處理時間)和改進(jìn)電路設(shè)計(jì),減少電容器漏電和晶體管的亞閾值電流,從而提升DRAM的可靠性。

性能:不斷優(yōu)化晶體管特性(如閾值電壓調(diào)整)和電容器材料(如高K介質(zhì)的應(yīng)用),提高DRAM的存儲速度和能效比。

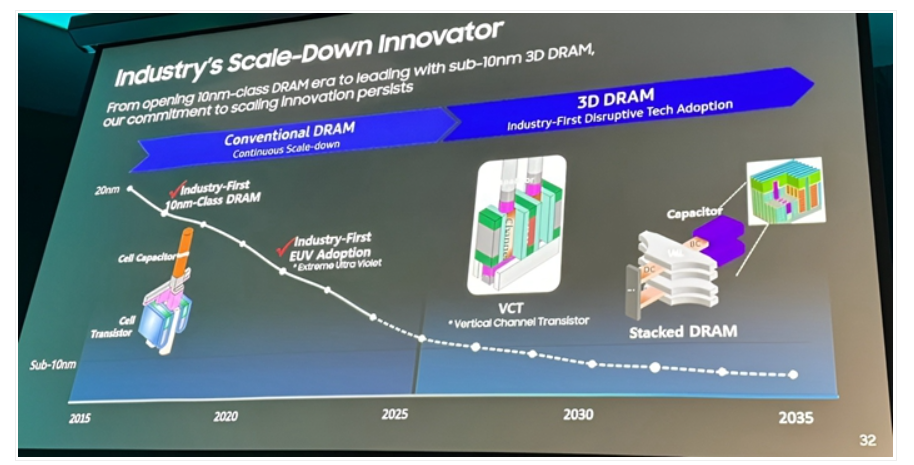

7. 未來的發(fā)展趨勢

3D DRAM是一種通過堆疊多個存儲層和使用垂直互聯(lián)技術(shù)來增加存儲密度和性能的先進(jìn)DRAM技術(shù)。

隨著3D集成技術(shù)的發(fā)展,DRAM正在從二維平面結(jié)構(gòu)向三維堆疊結(jié)構(gòu)演進(jìn),能夠在有限的面積內(nèi)集成更多的存儲單元,提高存儲密度。此外,低功耗和高速度將是未來DRAM技術(shù)發(fā)展的重要方向。

圖片來源:Samsung

友情鏈接:站點(diǎn)地圖 薩科微官方微博 立創(chuàng)商城-薩科微專賣 金航標(biāo)官網(wǎng) 金航標(biāo)英文站

Copyright ?2015-2025 深圳薩科微半導(dǎo)體有限公司 版權(quán)所有 粵ICP備20017602號