服務熱線

0755-83044319

發布時間:2025-03-04作者來源:薩科微瀏覽:877

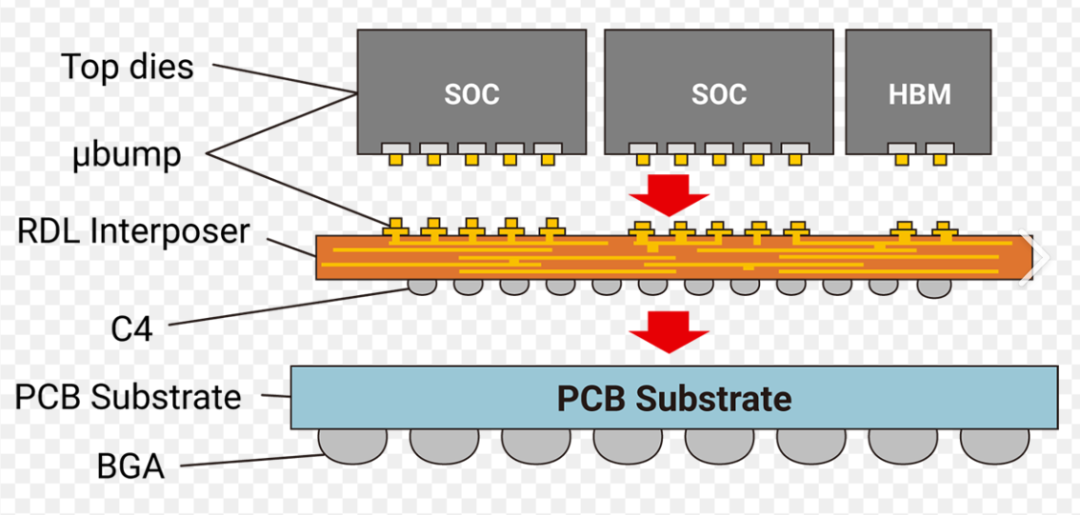

封裝中的RDL(Redistribution Layer,重分布層)是集成電路封裝設計中的一個重要層次,主要用于實現芯片內電氣連接的重新分配,并且在封裝中起到連接芯片和外部引腳之間的橋梁作用。RDL的設計和實現直接影響到封裝的電氣性能、可靠性和制造成本。

1. RDL的基本概念

RDL是指在芯片的封裝過程中,重新布置芯片表面上的信號線和電源線,以適應封裝基板的布局需求。簡單來說,它是芯片和封裝基板之間的電路層,起到信號引導和分配的作用。通過RDL,芯片內部的引腳可以被重新分布到基板上的不同位置,提供與外部系統連接的功能。

2. RDL的設計目標

信號分配

:RDL層的一個主要目標是將芯片的I/O(輸入/輸出)信號有效地分配到封裝的不同區域。這樣做可以優化信號傳輸路徑,減少信號延遲和串擾。

電源分布

:除了信號線的布置外,RDL還負責電源層的布置,確保芯片和封裝基板之間的電流穩定傳輸,避免過高的電流密度導致過熱或燒毀問題。

尺寸與性能平衡

:通過優化RDL的布局,設計師可以在保持小封裝尺寸的同時,滿足高性能的要求。這對于高集成度的芯片尤為重要。

3. RDL的設計步驟

RDL的設計通常包括以下幾個步驟:

信號分配分析:在設計RDL之前,首先要評估芯片內部的信號連接方式,分析每個I/O引腳的功能和其需要的連接路徑。通過與芯片設計團隊協作,確保信號線的最優布局。

布線設計:根據需求進行具體的RDL布線設計。RDL通常采用多層結構,通過不同層次的線路進行信號和電源的分配。設計時需要考慮布線路徑、走線長度、寬度、間距等,以優化電氣性能并避免信號干擾。

電氣性能仿真:在設計完成后,通過仿真工具對RDL進行電氣性能驗證。這包括信號完整性(SI)和電源完整性(PI)分析,確保高頻信號不會因布線不當產生衰減,電源分布穩定。

熱力分析與優化:由于高功率芯片會產生大量熱量,RDL的設計還需要進行熱力學分析。通過模擬熱流和散熱路徑,確保封裝內的溫度不會過高,避免對芯片性能產生負面影響。

制造與測試驗證:RDL設計完成后,進入制造階段。制造時需要根據設計圖紙進行多層基板的制作,并通過各種測試方法驗證RDL的電氣連接性和機械穩定性,確保封裝可以順利通過后續的可靠性測試。

4. RDL與封裝的關系

RDL層通常作為芯片封裝的核心組成部分,與其他封裝結構(如基板、外部引腳等)緊密配合。它不僅為芯片和封裝基板之間的連接提供了通路,還決定了封裝的電氣性能、散熱性能以及最終的封裝尺寸。

例如,像BGA(Ball Grid Array)或FCBGA(Flip Chip Ball Grid Array)封裝中,RDL負責將芯片的I/O引腳重分布到基板上的焊球位置,確保信號從芯片傳輸到封裝外部的電路板。

5. RDL的技術挑戰

多層結構復雜性

:RDL設計需要使用多層布線,這增加了設計的復雜性。設計師需要平衡信號傳輸質量、熱性能和機械穩定性等因素。

信號完整性問題

:隨著芯片頻率和集成度的增加,RDL中的信號完整性問題變得愈發嚴重。如何減少信號的損失、避免信號串擾、提高抗干擾能力是RDL設計的關鍵。

尺寸與成本控制

:在保證性能的前提下,RDL的設計需要盡量減少封裝的體積和制造成本。因此,如何通過優化布線來減小封裝尺寸,并確保成本可控,是設計過程中必須考慮的因素。

6. RDL的應用與發展趨勢

隨著集成電路技術的不斷進步,封裝的要求也越來越高。RDL技術在高性能芯片封裝中起著越來越重要的作用。尤其在像5G、AI、汽車電子等領域,對封裝的要求更是不斷提高。未來,RDL技術將朝著更高頻、更小尺寸、更低成本的方向發展,同時加強與熱管理、可靠性分析等其他封裝領域的協同設計。

總結。RDL是集成電路封裝中不可或缺的設計層,負責芯片與封裝之間的電氣連接與信號分配。它不僅影響封裝的電氣性能,還與封裝的尺寸、熱管理、成本等多個因素密切相關。隨著技術的發展,RDL設計正變得越來越復雜,要求設計師在保證性能的同時,還需優化尺寸、成本,并解決信號完整性等技術挑戰。

免責聲明:本文采摘自“老虎說芯”,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2025 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號