服務(wù)熱線

0755-83044319

發(fā)布時(shí)間:2024-08-13作者來源:薩科微瀏覽:1474

3納米工藝節(jié)點(diǎn)中的GAA晶體管帶來了顯著的技術(shù)挑戰(zhàn)。提取電氣特性需要新的方法和工具,以應(yīng)對(duì)其復(fù)雜的三維結(jié)構(gòu)和對(duì)工藝變異的敏感性。同時(shí),新的物理失效模式也需要在設(shè)計(jì)和制造過程中加以重視,以確保晶體管的可靠性和性能。3納米晶圓制造工藝中的“Gate all-around (GAA) transistors”所帶來的新提取要求和物理失效模式是一個(gè)復(fù)雜的問題。

1. 理解什么是“Gate all-around (GAA) transistors”。

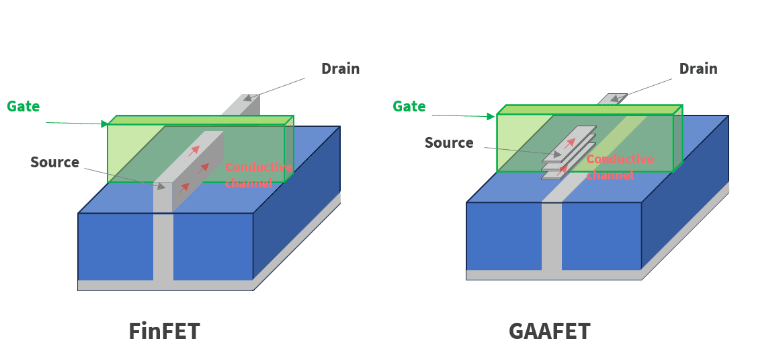

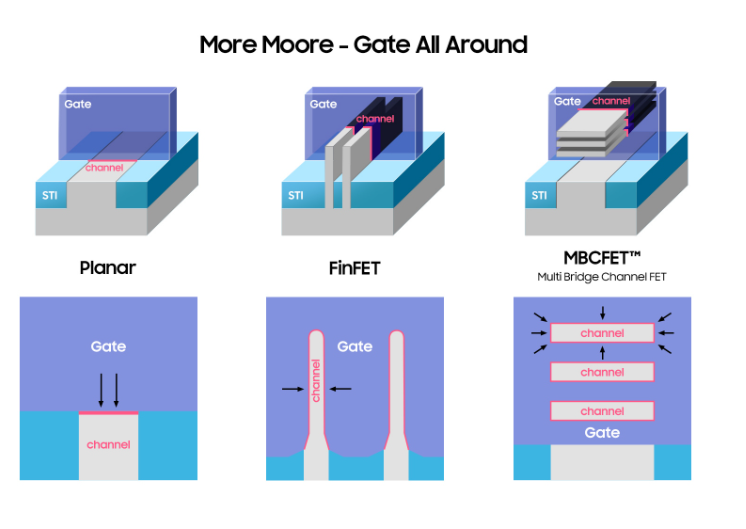

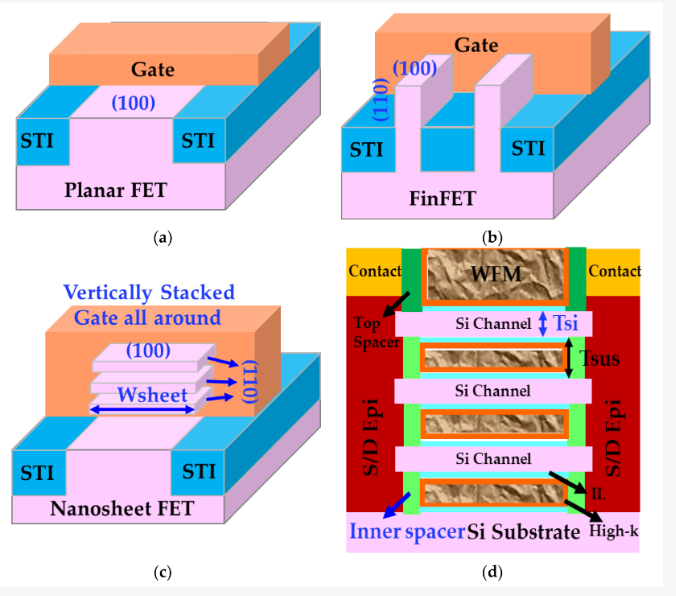

傳統(tǒng)的晶體管(FinFET):在10納米及以上的工藝節(jié)點(diǎn)中,F(xiàn)inFET是一種常見的晶體管結(jié)構(gòu)。在這種結(jié)構(gòu)中,柵極(Gate)圍繞著鰭狀結(jié)構(gòu)的三個(gè)側(cè)面進(jìn)行控制,類似于一個(gè)“U”字形包圍。

Gate all-around (GAA)晶體管:在更小的節(jié)點(diǎn)(如3納米)中,GAA晶體管進(jìn)一步優(yōu)化了FinFET的設(shè)計(jì)。柵極完全包圍著導(dǎo)電通道,從四個(gè)方向控制電流。這種設(shè)計(jì)可以更好地控制漏電流,并提高晶體管的性能和效率。

2. 挑戰(zhàn)一:GAA晶體管的結(jié)構(gòu)變化帶來了新的提取要求。

復(fù)雜的三維結(jié)構(gòu):由于柵極完全包圍通道,GAA晶體管具有比FinFET更復(fù)雜的三維結(jié)構(gòu)。這種復(fù)雜性使得提取電氣特性(如電容、電阻等)的難度大大增加。

精確建模:在設(shè)計(jì)和模擬過程中,需要精確建模GAA晶體管的電氣行為。這要求更復(fù)雜的計(jì)算方法和工具,以確保模型能夠準(zhǔn)確反映實(shí)際的晶體管性能。

工藝變異影響:GAA晶體管對(duì)制造過程中微小的工藝變異(如材料厚度、形狀不均勻等)更加敏感。這些變異會(huì)影響晶體管的電氣特性,因此在提取過程中需要特別關(guān)注這些細(xì)節(jié)。

3. 挑戰(zhàn)二:GAA晶體管的新結(jié)構(gòu)也引入了新的物理失效模式。

應(yīng)力集中:由于GAA晶體管的柵極完全包圍通道,在制造過程中可能會(huì)在某些區(qū)域產(chǎn)生應(yīng)力集中。這些應(yīng)力集中點(diǎn)可能導(dǎo)致材料疲勞或斷裂,影響晶體管的可靠性。

熱管理問題:GAA晶體管的密度更高,熱量更集中,這對(duì)晶圓的散熱能力提出了更高的要求。如果熱量無法有效散出,可能導(dǎo)致晶體管過熱失效。

界面缺陷:柵極和通道之間的界面更加復(fù)雜,這可能引入更多的界面缺陷。這些缺陷會(huì)影響電流的流動(dòng),導(dǎo)致晶體管性能下降,甚至失效。

圖:(a) 平面FET,(b) FinFET, (C)具有三個(gè)垂直堆疊硅通道的體型GAA NS FET,以及(d) 體型GAA NS FET的源漏區(qū)切面圖

免責(zé)聲明:本文采摘自“老虎說芯”,本文僅代表作者個(gè)人觀點(diǎn),不代表薩科微及行業(yè)觀點(diǎn),只為轉(zhuǎn)載與分享,支持保護(hù)知識(shí)產(chǎn)權(quán),轉(zhuǎn)載請(qǐng)注明原出處及作者,如有侵權(quán)請(qǐng)聯(lián)系我們刪除。

友情鏈接:站點(diǎn)地圖 薩科微官方微博 立創(chuàng)商城-薩科微專賣 金航標(biāo)官網(wǎng) 金航標(biāo)英文站

Copyright ?2015-2025 深圳薩科微半導(dǎo)體有限公司 版權(quán)所有 粵ICP備20017602號(hào)