服務熱線

0755-83044319

發(fā)布時間:2024-10-31作者來源:薩科微瀏覽:1117

低電壓模擬電路設計技術的核心是要在盡可能低的電源電壓下,實現高效的模擬信號處理。這種設計思路主要受到移動設備、植入式醫(yī)療設備等應用場景的需求驅動。由于這些設備的空間和能量資源有限,工程師們需要找到能夠在低電壓(如3V以下)下高效工作的電路設計方法。

1. 技術選擇與工藝背景

低電壓設計首先受到半導體工藝的限制。在標準的CMOS工藝中,晶體管的閾值電壓不會隨工藝尺寸縮小而成比例降低,這使得在低電壓下工作變得具有挑戰(zhàn)性。多閾值工藝、BiCMOS以及SOI(硅絕緣)技術可以在一定程度上克服這些限制,但通常成本較高。簡單地說,如果工藝選擇得當,工程師可以在低電壓下實現較好的電路性能,但需要權衡成本和復雜性。

2. 全區(qū)一體化晶體管模型

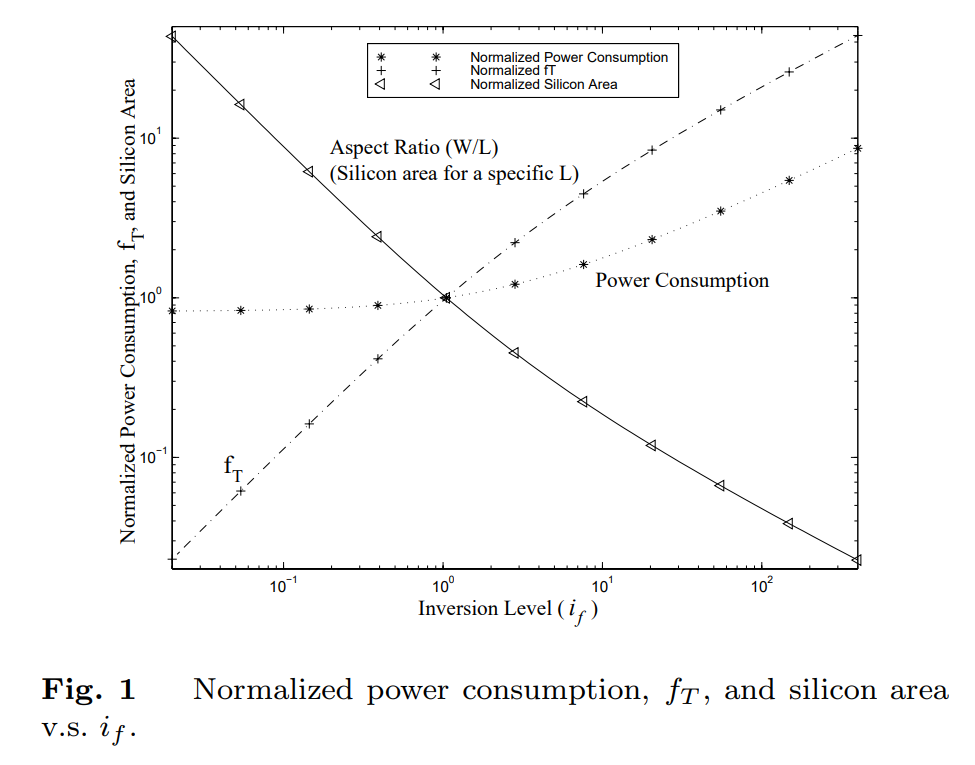

通常,晶體管在不同的偏置電壓下會呈現弱反型、強反型等不同的工作區(qū)域,每個區(qū)域都有不同的特性。例如,弱反型區(qū)域適合低功耗設計,但頻率響應較差,而強反型則能提供較好的速度,但耗電量較大。因此,工程師們開發(fā)了“一體化模型”,這個模型可以在所有工作區(qū)間內提供連續(xù)的性能指標,從而幫助設計工程師更輕松地優(yōu)化電路性能,在功耗、頻率響應和面積之間找到[敏感詞]平衡。

3. 降低電源需求的電路策略

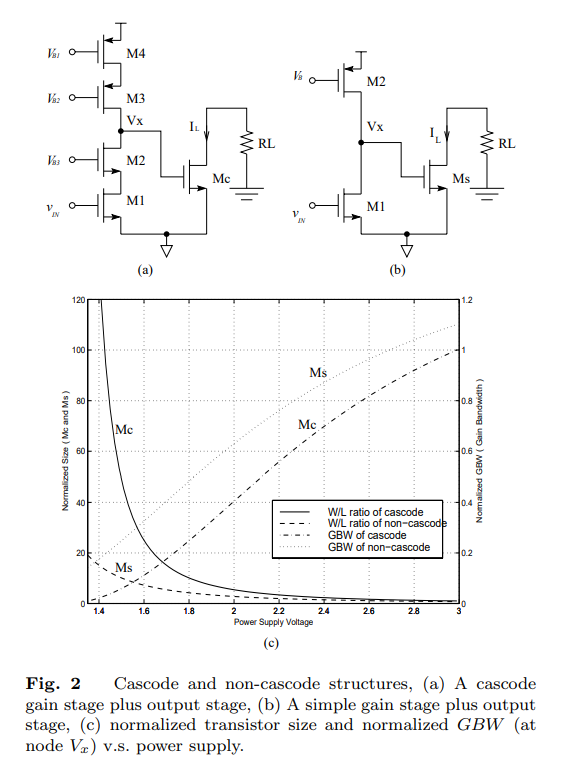

在低電壓環(huán)境中,傳統(tǒng)的級聯(lián)結構由于“電壓余量”不足而難以實現。級聯(lián)結構類似于“高樓”,通過“堆疊”晶體管來提高輸出阻抗,但在低電壓下無法疊加。相反,工程師們采用“水平擴展”的策略,用更簡單的非級聯(lián)結構來實現高增益。這有點像在地面上建多層平房,而不是高樓,這樣既節(jié)省電壓余量,又確保電路穩(wěn)定。

4. 全差分和平衡結構

在低電壓設計中,全差分或平衡電路結構被廣泛應用,因為它們具有更好的抗共模干擾(CMRR)和電源抑制比(PSRR),并且能夠擴大信號擺幅。可以把它比作“橋梁的兩邊各行車道”的設計,電流可以更高效、更平穩(wěn)地流過橋梁,避免了單邊行車帶來的干擾和不穩(wěn)定。

5. 低電壓下的關鍵構建模塊

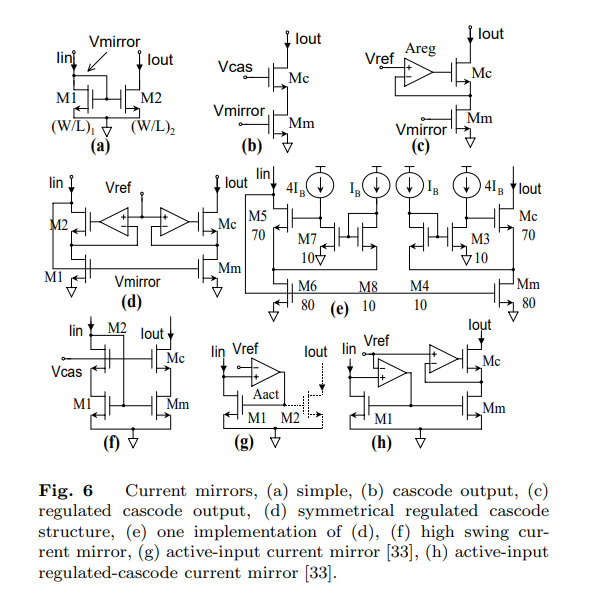

低電壓設計的核心模塊包括電流鏡、差分對和Class AB輸出結構等,它們是低電壓電路的基礎單元。例如,電流鏡在低電壓下需要創(chuàng)新設計以保證穩(wěn)定的輸出,而差分對則用于提高信號的線性度。這些基礎模塊就像樂高積木,通過不同的拼接組合,可以實現各種功能復雜的電路。

6. 特殊晶體管技術

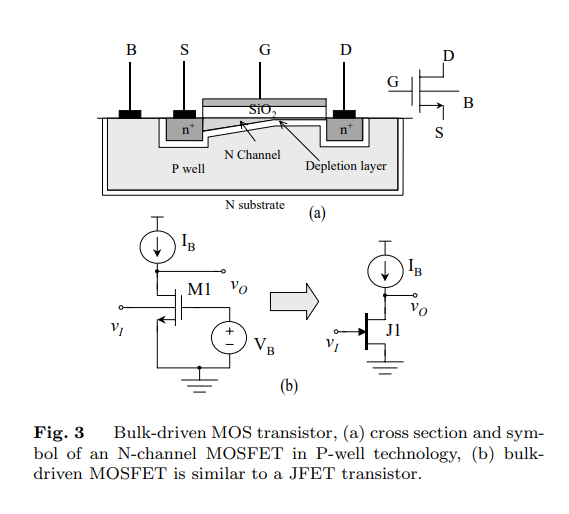

在低電壓下,傳統(tǒng)晶體管的驅動電壓不足以有效工作,因此采用了兩種特殊技術——體驅動和浮柵技術:

體驅動MOSFET:它通過將信號輸入到晶體管的襯底(bulk)而不是柵極(gate),類似于給房間增加另一個門,提升了低電壓下的性能,但同時降低了增益和頻率響應。

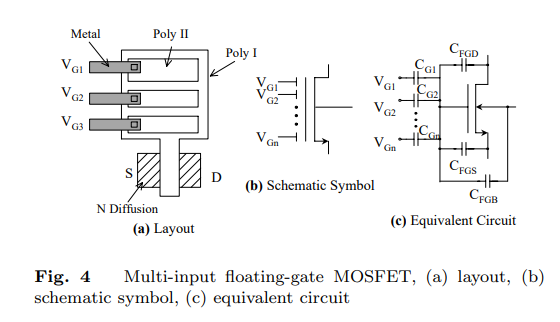

浮柵MOSFET:這種結構可以在多個輸入端與浮動的柵極之間建立電容耦合,實現有效的信號控制,類似于用“遙控器”調節(jié)晶體管的工作狀態(tài),以節(jié)省電源電壓需求。

7. 多級頻率補償

低電壓多級放大器通常需要特別的頻率補償策略,以確保電路的穩(wěn)定性。由于多級電路中會出現多個頻率極點,這些極點可能導致系統(tǒng)不穩(wěn)定,因此通過巧妙地調節(jié)極點和零點的位置,使電路在閉環(huán)狀態(tài)下保持穩(wěn)定。可以把頻率補償想象成一個多層過濾系統(tǒng),逐級去除不必要的噪聲,使信號清晰、穩(wěn)定地傳遞到輸出端。

8. 動態(tài)范圍的挑戰(zhàn)

在低電壓環(huán)境中,由于信號擺幅和電源電壓都減小,電路的動態(tài)范圍會下降。工程師們通過改進電路設計,努力確保信號的[敏感詞]擺幅在給定的噪聲限制內。這有點類似于減少音量限制下,力求在不失真的前提下獲得[敏感詞]的音質。

9. 低電壓開關電容電路

在低電壓下實現開關電容電路也非常具有挑戰(zhàn)性,尤其是在信號路徑中驅動關鍵開關時。常用的解決方案包括使用低閾值MOS器件、時鐘電壓倍增或開關運放技術,但它們各有局限,例如成本較高、頻率響應受限等。

小結一下,低電壓模擬電路設計是一個在電壓、功耗、頻率響應和面積等多個維度上取得平衡的過程。工程師們通過創(chuàng)新設計方法,例如一體化晶體管模型、體驅動和浮柵技術、多級頻率補償等,不斷克服低電壓環(huán)境中的種種挑戰(zhàn)。

免責聲明:本文采摘自“老虎說芯”,本文僅代表作者個人觀點,不代表薩科微及行業(yè)觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯(lián)系我們刪除。

友情鏈接:站點地圖 薩科微官方微博 立創(chuàng)商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2025 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號