服務熱線

0755-83044319

發布時間:2023-03-27作者來源:電子創新網瀏覽:2044

3月17日,業內知名 EDA 解決方案專家、2004年成立的思爾芯S2C在深圳舉行媒體溝通會,思爾芯S2C總裁兼CEO林俊雄先生向電子創新網等知名媒體介紹了思爾芯[敏感詞]推出的企業級國產硬件仿真系統——OmniArk芯神鼎。

據他介紹,OmniArk芯神鼎是真正的國產硬件仿真系統,對標國際三巨頭,可實現信號全可視的產品,此外,OmniArk芯神鼎擁有自主研發核心技術,實現了對超大規模設計的全自動編譯,另據他透露,思爾芯已經有豐富的產品線并在功能驗證完整布局,如今已邁入數字前端驗證全流程。

思爾芯S2C資深副總裁李艷榮給媒體介紹了這款產品的應用背景和具體性能指標。

|詳解企業級國產硬件仿真系統——OmniArk芯神鼎

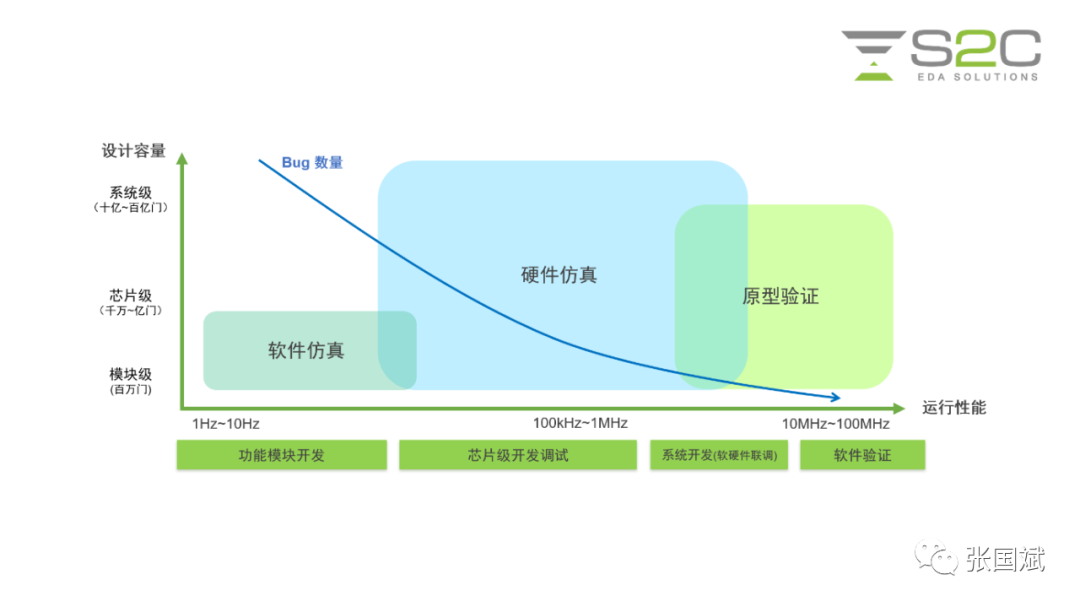

我們都知道,在芯片的研發中,風險主要來自芯片的正確性代價成本。如何在流片前及時、徹底地發現設計中潛藏的邏輯錯誤,保證芯片的可用性、高效性、始終是業內著力解決的問題。因此驗證在芯片設計與實現中是非常重要的一環,這些復雜芯片的開發都需要進行更全面的測試驗證。在數字電路設計的早期,設計和驗證團隊往往會選擇軟件仿真、硬件仿真及原型驗證作為常規驗證工具。

業內人士通常將硬件仿真作為調試的大殺器,尤其在面對SoC中硬件和軟件的交互。硬件仿真有著比軟仿更高的運算能力再加上全可視的特點, 能夠更有效地發現缺陷并提供調試和修正手段,解決嵌入式硬件和軟件底層邊界之間的疑難雜癥。

因為硬件仿真往往具有以下特點:

● 設計容量大,可擴展性好

● 仿真速度快

● 調試能力強,調試模式多樣

● 適合大型設計從模塊級、芯片級到系統級的仿真驗證

由于大數據處理及AI芯片設計規模的持續擴大,以及市場激烈競爭下的快速迭代需求,越來越多的芯片設計公司考慮選擇硬件仿真系統,來提高芯片驗證效率,縮短芯片開發周期。而硬件仿真成為平臺化中心的特點也越來越明顯。

|企業級硬件仿真系統新突破

伴隨各種設計驗證方法學的不斷推陳出新,各種硬件仿真系統也層出不窮。在硬件仿真的選擇中,通常會考核很多功能,硬件仿真系統的執行速度,硬件可靠性,是否有更大的設計容量,及多用戶資源等,都是芯片設計公司選擇時會考慮的多重因素。另外,還會考慮是否有其他新特性,來不斷提高這種驗證技術的投資回報率。例如:

● 如何快速搭建驗證環境,在極短時間內完成用戶設計的移植和部署

● 如何快速發現和定位深層次的隱藏問題

● 如何快速設計足夠驗證case,滿足不同應用場景的驗證需求

● 如何在短時間完成對大規模設計的充分驗證

針對復雜芯片規模的驗證痛點,業界普遍認為先進的企業級硬件仿真系統還應有更大的突破,例如:

● 需要操作便捷,系統自動化程度高,支持用戶設計的全自動編譯,無需對設計過多干預,Gigabyte級別的設計網表能快速編譯并快速完成后端工作

● 需要具有強大的調試能力,支持足夠靈活的調試手段,可以捕捉源代碼的深度錯誤和性能瓶頸。在實現高速運轉速度的同時保證信號全部可探測(信號全可視),支持靈活的實時觸發、海量的波形數據存儲和分析

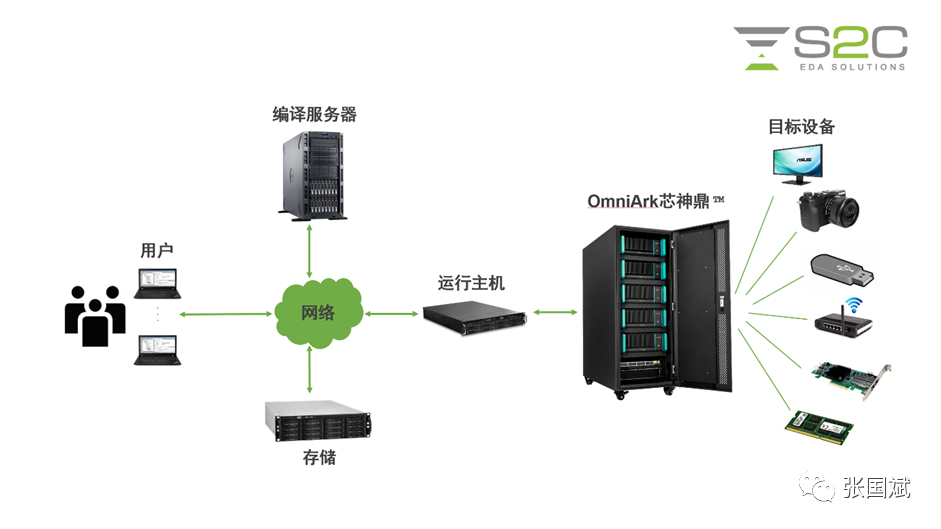

為了滿足日益復雜的芯片設計,以及日益旺盛的國產化需求,思爾芯全新推出 「OmniArk 芯神鼎」企業級硬件仿真系統。該產品為思爾芯自主研發,擁有多項自主知識產權的核心技術,實現了對超大規模設計的全自動編譯。目前已在多個芯片設計企業推廣使用。幫助汽車電子、CPU、AI、5G、云計算等SoC設計所需的復雜驗證。

該產品采用超大規模商用可擴展陣列架構設計,機箱模塊結構,方便維護和擴展。產品形態從桌面型到機柜型,設計容量可擴展至20億門。包含一套便捷易用的軟件系統,支持GUI圖形界面和TCL腳本命令,集成編譯、運行、調試的完整流程。

|OmniArk 芯神鼎重要特性

“工欲善其事,必先利其器”, OmniArk 芯神鼎在提供硬件加速平臺的同時也提供各種功能的創新配套軟件:用戶設計語法自動糾錯、Smart P&R技術,ABS(Auto-Block Select)技術, ?多樣化信號采集手段等等,讓用戶實現MHz級仿真加速、全自動智能編譯流程、強大調試能力,以及多種仿真驗證模式。更擁有豐富的VIP庫,適合超大規模高端通用芯片設計的系統級驗證,可以滿足不同驗證場景需求。

重要特性:

1、設計快速移植和部署

● 支持Verilog,SystemVerilog等常用開發語言

● 用戶設計語法自動糾錯

● 自動化的門控時鐘、三態、多驅等處理

2、全自動智能編譯流程

● 多線程(進程)并行綜合;

● 超大規模的用戶內存自動建模映射

● 多時鐘域時序分析,運行頻率估算

● Smart P&R技術,幫助參數智能優化

● 增量編譯,減少編譯時間

選擇高性能的軟件開發工具往往能夠大大提高硬件仿真的驗證效率。OmniArk芯神鼎整個編譯流程皆為全自動,較少需要用戶干預,通過多種核心技術,就能實現快速編譯與自由設計。

3、MHz級仿真加速

● 時序驅動的分割和路由算法:兼顧最小切割和關鍵路徑延時

● 時序驅動的TDM和引腳分配:關鍵路徑采用更小的Ratio比

● 系統級時序建模及時序分析:準確估算[敏感詞]運行頻率、為時序驅動算法提供反饋

● ABS(Auto-Block Select)技術:解決超大規模設計的性能挑戰

對硬件仿真工具的性能影響[敏感詞]的是基本元件之間的連接延遲,因此分割(Partitioning)對仿真速度的影響[敏感詞]。以一個10億門的超大規模電路設計為例,如果將其在專用的硬件仿真平臺上,就會涉及到的芯片間切割、布線、時序分析等一系列復雜問題。傳統的分割器只優化切割數(Sum of External Degrees),所以不能有效的優化時序(Timing),因此應用時序驅動的分割器來提高硬件仿真性能。OmniArk芯神鼎采用4大技術創新,其中通過時序驅動的分割和路由算法,兼顧最小切割和關鍵路徑延時,可實現高達數MHz的仿真速度,從而提高硬件仿真性能。

4、強大的調試糾錯能力

● 多樣化信號采集手段

● 靈活設置信號觸發方式

● 支持存儲器后門讀寫,為固件的裝載和調試提供便利

● 支持Force/Release/Deposit,方便進行故障注入測試

芯神鼎有著多樣化信號采集手段,比如:靜態探針,動態探針,信號全可視(IO/Register/Logic/Memory),更有靈活設置信號觸發方式,支持對任意信號的波形實時抓取。此外還支持存儲器后門讀寫,可以為固件的裝載和調試提供便利;支持Force/Release/Deposit,方便進行故障注入測試;并且內置了波形查看工具,并支持波形與RTL代碼反標,方便在RTL源碼級調試,使得整個調試糾錯能力更高效。

5、多種仿真驗證模式

芯神鼎擁有多種的仿真驗證模式,如TBA、ICE、QEMU等模式,滿足多種驗證場景的需求。

6、豐富的VIP庫

芯神鼎擁有豐富的VIP庫,支持常見高性能接口的速度適配,如AHB、AXI、PCIe、DDR、Ethernet、USB等,可以滿足不同驗證場景需求。

|OmniArk 芯神鼎應用案例

電子科技大學(成電)和西安電子科技大學在使用了 OmniArk 芯神鼎后,表達了對產品的高度認可。

西安電子科技大學微電子學院教授游海龍表示:“西電在采購建設世界先進 EDA 工具的同時,支持國產[敏感詞] EDA 研發成果。2022 年,我們采購了國產自主研發的 OmniArk 芯神鼎,并在我校集成電路設計教學與科研中發揮了重要作用。在面向先進集成電路設計研發驗證中,基于 OmniArk 芯神鼎上實現了快速移植和部署,提前計劃完成了工程搭建,無需對硬件環境進行手工連線。整個全自動的智能編譯流程能夠大大提高我們的驗證效率,調試能力強大且靈活,用戶界面操作友好且易用,幫助我們在超大規模 SoC 設計中系統級功能驗證的實現。同時 OmniArk 芯神鼎的高性能和易操作也支持著我們的課堂教學,實踐教學,課程設計等教學活動, 使教學效果出現了非常大的改觀。”

OmniArk 芯神鼎是西電首臺購買并應用于教學的硬件仿真工具,也是基于國產自主的突破性 EDA 工具,使得相關成果能在國內高校得到應用,為西電集成電路設計方面人才培養提供了有利條件。

游教授進一步表示:“依托西電產教融合創新平臺,我們將為 OmniArk 芯神鼎在國內開展實訓。并與思爾芯圍繞集成電路驗證領域,進一步緊密合作,依托硬件平臺合作共建教材、課程,為我國建設培養更多掌握先進設計方法學以及國產自主工具的高層次人才。”

|結合其他產品線打造全流程

OmniArk 芯神鼎是真正的國產企業級硬件仿真系統,對標三巨頭,實現信號全可視的產品。

思爾芯自 2004 年成立以來一直專注于 EDA 領域的深耕發展。近 20 年雄厚的技術積累,使得產品成熟、穩定,表現也更為出色,多年來深受市場的肯定。尤其是在中國 IC 設計公司數量越來越多的大環境下,還能夠做到充分貼近本地客戶服務,最終獲得越來越多的客戶認可和信任。

基于思爾芯能夠深入挖掘客戶痛點,不斷快速響應的服務特點,得到了600+的海內外客戶背書。此次新產品的開發就是為了響應龐大而豐富的客戶群體需求,打造了國產化、自動化、高性能、真正全可視的調試環境,幫助客戶完成驗證場景,提高整個芯片開發效率,加速產品上市周期。

思爾芯目前已完善了整個芯片設計的功能驗證布局,提供了成熟商用的架構設計軟件、高性能多語言混合的數字軟件仿真工具、企業級國產硬件仿真系統、多組合方案的原型驗證解決方案等。

未來,思爾芯還將結合其他產品線,通過獨立的硬件仿真配上幫助與軟件仿真、原型驗證協同仿真的軟件,一樣可以實現軟硬件協同仿真的完美運行。以先進的異構驗證方法學進行 SoC 設計,打造出真正的國產數字 EDA 全流程。

思爾芯(S2C)自2004年設立上海總部以來始終專注于集成電路EDA領域。作為業內知名的 EDA 解決方案專家,公司業務聚焦于數字芯片的前端驗證,已覆蓋驗證云服務、架構設計、軟件仿真、硬件仿真、原型驗證等工具。已與超過600家國內外企業建立了良好的合作關系,服務于人工智能、超級計算、圖像處理、數據存儲、信號處理等數字電路設計功能的實現,廣泛應用于物聯網、云計算、5G通信、智慧醫療、汽車電子等終端領域。

公司總部位于上海,并建立了全球化的技術研發與市場服務網絡,在北京、深圳、西安、香港、東京、首爾及圣何塞等地均設有分支機構或辦事處。

思爾芯在EDA領域的技術實力受到了業界的廣泛認可,通過多年耕耘,已在原型驗證領域構筑了技術與市場的雙優勢地位。并參與了我國EDA團體標準的制定,承擔了多項國家及地方重大科研項目。

免責聲明:本文采摘自“電子創新網”,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2025 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號