服務(wù)熱線

0755-83044319

發(fā)布時(shí)間:2022-04-02作者來(lái)源:大印藍(lán)海科技瀏覽:20597

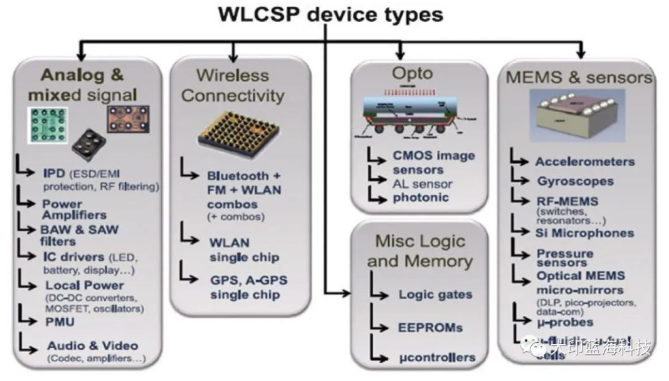

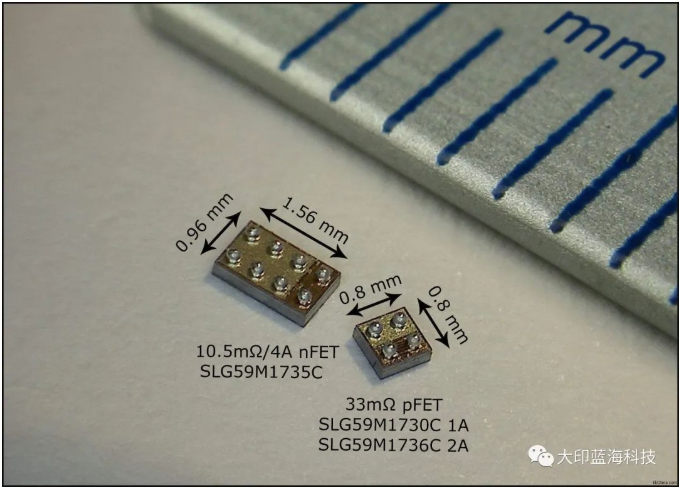

WLCSP(Wafer Level Chip Scale Packaging)是一種晶圓級(jí)芯片封裝方式,有別于傳統(tǒng)的芯片封裝方式(切割、封裝、測(cè)試,封裝后原始芯片數(shù)量會(huì)增加至少20%)。 整個(gè)晶圓封裝測(cè)試后,切割成單個(gè)IC顆粒,因此封裝體積與IC裸片原始尺寸相同。 WLCSP封裝方式不僅顯著減小了內(nèi)存模塊的尺寸,還滿足了移動(dòng)設(shè)備對(duì)體空間的高密度要求。 另一方面,在性能方面,也提升了數(shù)據(jù)傳輸?shù)乃俣群头€(wěn)定性。

WLCSP的特性優(yōu)點(diǎn)

-原芯片尺寸最小封裝方式:

WLCSP晶圓級(jí)芯片封裝方式的[敏感詞]特點(diǎn)便是有效地縮減封裝體積,故可搭配于行動(dòng)裝置上而符合可攜式產(chǎn)品輕薄短小的特性需求。

-數(shù)據(jù)傳輸路徑短、穩(wěn)定性高:

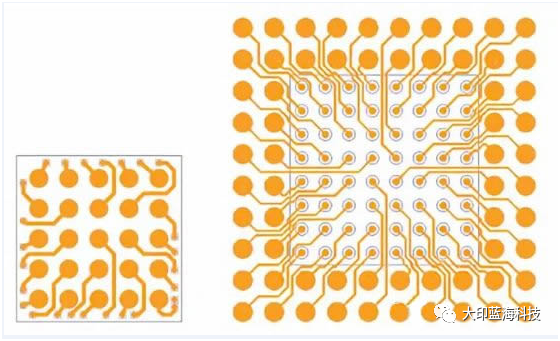

采用WLCSP封裝時(shí),由于電路布線的線路短且厚(標(biāo)示A至B的黃線),故可有效增加數(shù)據(jù)傳輸?shù)念l寛減少電流耗損,也提升數(shù)據(jù)傳輸?shù)姆€(wěn)定性。

散熱特性佳

由于WLCSP少了傳統(tǒng)密封的塑料或陶瓷包裝,故IC芯片運(yùn)算時(shí)的熱能便能有效地發(fā)散,而不致增加主機(jī)體的溫度,而此特點(diǎn)對(duì)于行動(dòng)裝置的散熱問(wèn)題助益極大。

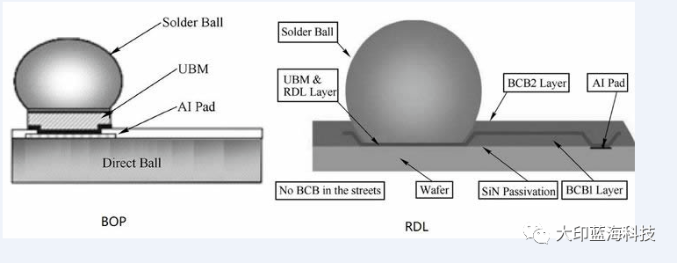

WLCSP可以被分成兩種結(jié)構(gòu)類型:直接BOP(bump On pad)和重新布線(RDL)。

BOP即錫球直接長(zhǎng)在die的Al pad上,而有的時(shí)候,如果出現(xiàn)引出錫球的pad靠的較近,不方便出球,則用重新布線(RDL)將solder ball引到旁邊。

最早的WLCSP是Fan-In,bump全部長(zhǎng)在die上,而die和pad的連接主要就是靠RDL的metal line,封裝后的IC幾乎和die面積接近。Fan-out,bump可以長(zhǎng)到die外面,封裝后IC也較die面積大(1.2倍)。

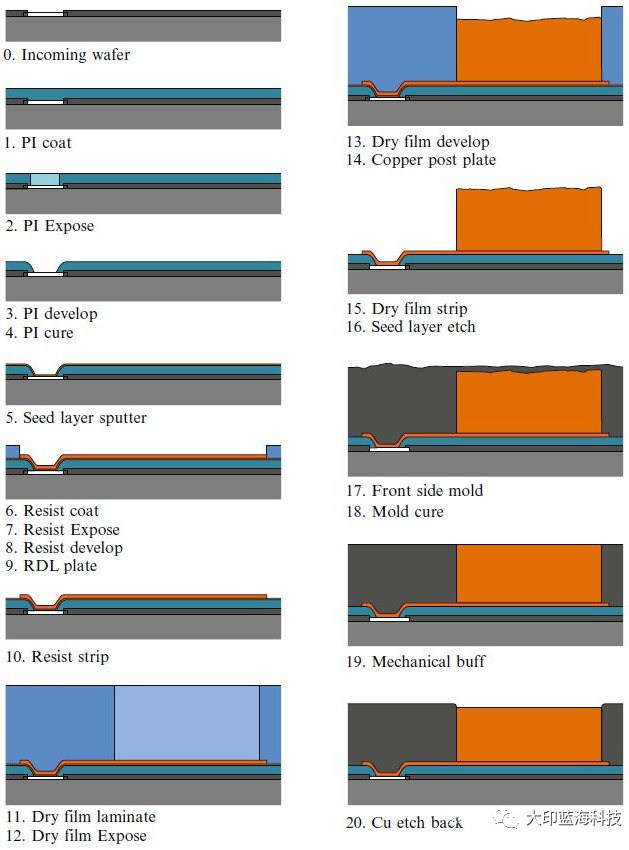

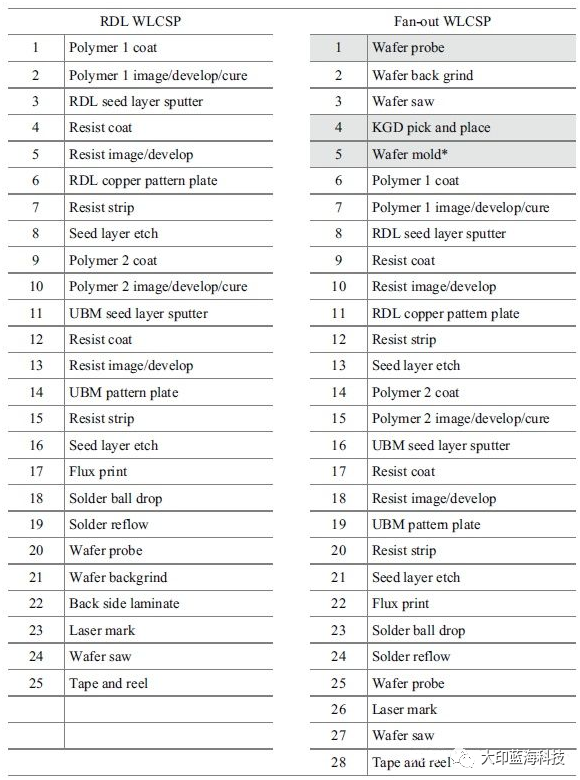

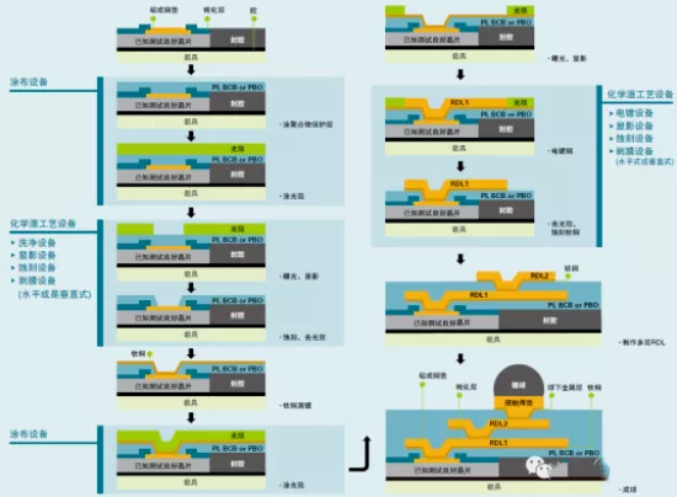

Fan-in: 如下流程為Fan-in的RDL制作過(guò)程。

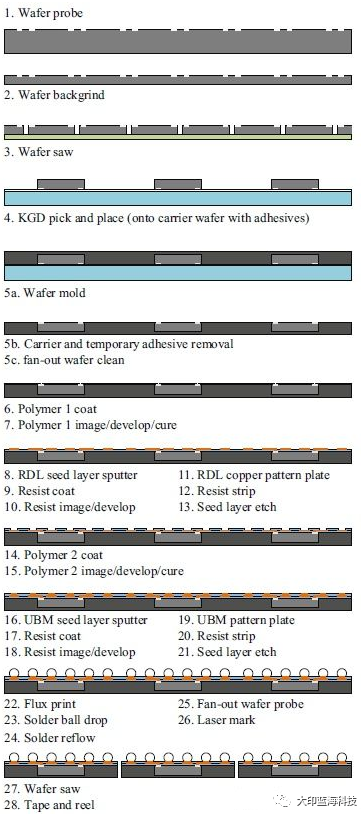

Fan-Out: 先將die從晶圓上切割下來(lái),倒置粘在載板上(Carrier)。此時(shí)載板和die粘合起來(lái)形成了一個(gè)新的wafer,叫做重組晶圓(Reconstituted Wafer)。在重組晶圓中,再曝光長(zhǎng)RDL。

Fan-in和Fan-out 對(duì)比如下,從流程上看,F(xiàn)an-out除了重組晶圓外,其他步驟與Fan-in RDL基本一致。

延展閱讀

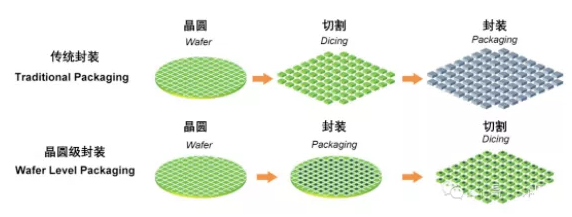

一、WLP晶圓級(jí)封裝VS傳統(tǒng)封裝

在傳統(tǒng)晶圓封裝中,是將成品晶圓切割成單個(gè)芯片,然后再進(jìn)行黏合封裝。不同于傳統(tǒng)封裝工藝,晶圓級(jí)封裝是在芯片還在晶圓上的時(shí)候就對(duì)芯片進(jìn)行封裝,保護(hù)層可以黏接在晶圓的頂部或底部,然后連接電路,再將晶圓切成單個(gè)芯片。

相比于傳統(tǒng)封裝,晶圓級(jí)封裝具有以下優(yōu)點(diǎn):

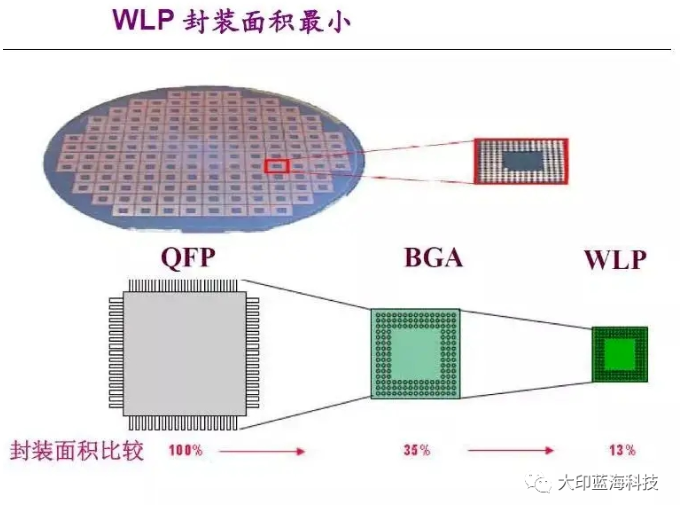

1、封裝尺寸小

由于沒(méi)有引線、鍵合和塑膠工藝,封裝無(wú)需向芯片外擴(kuò)展,使得WLP的封裝尺寸幾乎等于芯片尺寸。

2、高傳輸速度

與傳統(tǒng)金屬引線產(chǎn)品相比,WLP一般有較短的連接線路,在高效能要求如高頻下,會(huì)有較好的表現(xiàn)。

3、高密度連接

WLP可運(yùn)用數(shù)組式連接,芯片和電路板之間連接不限制于芯片四周,提高單位面積的連接密度。

4、生產(chǎn)周期短

WLP從芯片制造到、封裝到成品的整個(gè)過(guò)程中,中間環(huán)節(jié)大大減少,生產(chǎn)效率高,周期縮短很多。

5、工藝成本低

WLP是在硅片層面上完成封裝測(cè)試的,以批量化的生產(chǎn)方式達(dá)到成本最小化的目標(biāo)。WLP的成本取決于每個(gè)硅片上合格芯片的數(shù)量,芯片設(shè)計(jì)尺寸減小和硅片尺寸增大的發(fā)展趨勢(shì)使得單個(gè)器件封裝的成本相應(yīng)地減少。WLP可充分利用晶圓制造設(shè)備,生產(chǎn)設(shè)施費(fèi)用低。

二、晶圓級(jí)封裝的工藝流程

WLP工藝流程

晶圓級(jí)封裝工藝流程如圖所示:

1、涂覆[敏感詞]層聚合物薄膜,以加強(qiáng)芯片的鈍化層,起到應(yīng)力緩沖的作用。聚合物種類有光敏聚酰亞胺(PI)、苯并環(huán)丁烯(BCB)、聚苯并惡唑(PBO)。

2、重布線層(RDL)是對(duì)芯片的鋁/銅焊區(qū)位置重新布局,使新焊區(qū)滿足對(duì)焊料球最小間距的要求,并使新焊區(qū)按照陣列排布。光刻膠作為選擇性電鍍的模板以規(guī)劃RDL的線路圖形,最后濕法蝕刻去除光刻膠和濺射層。

3、涂覆第二層聚合物薄膜,是圓片表面平坦化并保護(hù)RDL層。在第二層聚合物薄膜光刻出新焊區(qū)位置。

4、凸點(diǎn)下金屬層(UBM)采用和RDL一樣的工藝流程制作。

5、植球。焊膏和焊料球通過(guò)掩膜板進(jìn)行準(zhǔn)確定位,將焊料球放置于UBM上,放入回流爐中,焊料經(jīng)回流融化與UBM形成良好的浸潤(rùn)結(jié)合,達(dá)到良好的焊接效果。

三、晶圓級(jí)封裝的發(fā)展趨勢(shì)

隨著電子產(chǎn)品不斷升級(jí)換代,智能手機(jī)、5G、AI等新興市場(chǎng)對(duì)封裝技術(shù)提出了更高要求,使得封裝技術(shù)朝著高度集成、三維、超細(xì)節(jié)距互連等方向發(fā)展。晶圓級(jí)封裝技術(shù)可以減小芯片尺寸、布線長(zhǎng)度、焊球間距等,因此可以提高集成電路的集成度、處理器的速度等,降低功耗,提高可靠性,順應(yīng)了電子產(chǎn)品日益輕薄短小、低成本的發(fā)展要需求。

晶圓級(jí)封裝技術(shù)要不斷降低成本,提高可靠性水平,擴(kuò)大在大型IC方面的應(yīng)用:

1、通過(guò)減少WLP的層數(shù)降低工藝成本,縮短工藝時(shí)間,主要是針對(duì)I/O少、芯片尺寸小的產(chǎn)品。

2、通過(guò)新材料應(yīng)用提高WLP的性能和可靠度。主要針對(duì)I/O多、芯片尺寸大的產(chǎn)品。

免責(zé)聲明:本文轉(zhuǎn)載自“大印藍(lán)海科技”,本文僅代表作者個(gè)人觀點(diǎn),不代表薩科微及行業(yè)觀點(diǎn),只為轉(zhuǎn)載與分享,支持保護(hù)知識(shí)產(chǎn)權(quán),轉(zhuǎn)載請(qǐng)注明原出處及作者,如有侵權(quán)請(qǐng)聯(lián)系我們刪除。

友情鏈接:站點(diǎn)地圖 薩科微官方微博 立創(chuàng)商城-薩科微專賣 金航標(biāo)官網(wǎng) 金航標(biāo)英文站

Copyright ?2015-2025 深圳薩科微半導(dǎo)體有限公司 版權(quán)所有 粵ICP備20017602號(hào)